# AOFG018V10GA1

Product Summary at T<sub>1</sub> = 25°C

$V_{DS. max}$

I<sub>DS, pulse</sub>

$R_{DS(on), max} @ V_{GS} = 5V$

$Q_{g, typ}$  @  $V_{DS} = 50V$

Qoss @ VDS = 50V

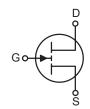

100V GaN Enhancement-mode Power Transistor

100V

$1.8 m\Omega$

19nC

580A

100nC

#### **Features**

- · GaN-on-Silicon E-mode HEMT technology

- Very low gate charge

- · Ultra low On-resistance

- · Very small footprint

## **Applications**

- High frequency DC/DC converter

- · High density DC/DC power module

- Synchronous rectification

- Motor driver

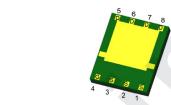

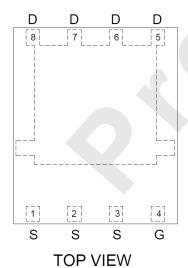

#### **Pin Configuration**

#### **Pin Information**

| Gate | Drain | Source  |

|------|-------|---------|

| 4    | 5-8   | 1, 2, 3 |

### **Ordering Information**

| Ordering Part Number | Package Type     | Form          | Shipping Quantity |

|----------------------|------------------|---------------|-------------------|

| AOFG018V10GA1        | En-FCLGA 5mm×6mm | Tape and Reel | 1500              |

#### Contact local sales office for full product datasheet.

#### **Absolute Maximum Ratings**

(T<sub>J</sub> = 25°C, unless otherwise noted)

| Symbol                    |                                    | AOFG018V10GA1                                                             | Units      |    |  |

|---------------------------|------------------------------------|---------------------------------------------------------------------------|------------|----|--|

| V <sub>DS</sub>           | Drain-source voltage               |                                                                           | 100        | V  |  |

| V <sub>DS(tr)</sub>       | Drain-source voltage transient (1) | V <sub>GS</sub> = 0V , 1h total time, T <sub>A</sub> = T <sub>JMAX</sub>  | 120        | V  |  |

|                           |                                    | $V_{GS} = 5V$ , $T_C = 25^{\circ}C$ , $R_{\theta JC} = 0.2^{\circ}C/W$    | 495        |    |  |

| 1                         | Continuous current                 | $V_{GS} = 5V$ , $T_{C} = 100^{\circ}C$ , $R_{\theta JC} = 0.2^{\circ}C/W$ | 313        | А  |  |

| <sup>I</sup> D            |                                    | V <sub>GS</sub> = 5V, T <sub>A</sub> = 25°C, R <sub>θJA</sub> = 38.1°C/W  | 35         |    |  |

|                           | Pulsed                             | T <sub>J</sub> = 25°C, T <sub>PULSE</sub> = 300µs                         | 580        |    |  |

| V                         | Gate-source voltage                |                                                                           | 6          | V  |  |

| V <sub>GS</sub> Gate-soul | Gate-source voltage                |                                                                           | -4         | V  |  |

| P <sub>tot</sub>          | Power dissipation                  | $V_{GS} = 5V$ , $T_C = 25^{\circ}C$ , $R_{\theta JC} = 0.2^{\circ}C/W$    | 442        | W  |  |

| ' tot                     |                                    | V <sub>GS</sub> = 5V, T <sub>A</sub> = 25°C, R <sub>θJA</sub> = 38.1°C/W  | 2.2        |    |  |

| T <sub>J</sub>            | Operating temperature              |                                                                           | -40 to 150 | °C |  |

| T <sub>STG</sub>          | Storage temperature                |                                                                           | -55 to 150 | °C |  |

#### **Thermal Characteristics**

| Symbol            | Parameter                                  | Тур  | Note | Units |

|-------------------|--------------------------------------------|------|------|-------|

| $R_{\theta JC}$   | Thermal resistance junction-to-case        | 0.2  |      | °C/W  |

| $R_{\theta JB}$   | Thermal resistance junction-to-board       | 2.2  |      | °C/W  |

| $R_{\theta JA}$   | Thermal resistance junction-to-ambient (2) | 38.1 |      | °C/W  |

| T <sub>sold</sub> | Maximum reflow soldering temperature       | 260  | MSL3 | °C    |

#### **Electrical Characteristics**

(T<sub>1</sub> = 25°C, unless otherwise noted)

| , 1 <sub>J</sub> – 25 C, u | filess otherwise floted)             |                                                                            |          |      |     |       |

|----------------------------|--------------------------------------|----------------------------------------------------------------------------|----------|------|-----|-------|

| Symbol                     | Parameter                            | Conditions                                                                 | Min      | Тур  | Max | Units |

| STATIC PA                  | RAMETERS                             |                                                                            |          |      |     |       |

| I <sub>DSS</sub>           | Drain-source leakage current         | V <sub>DS</sub> = 100V, V <sub>GS</sub> = 0V                               |          | 2.5  | 200 |       |

|                            |                                      | $V_{DS} = 100V, V_{GS} = 0V$ $T_{J} = 125^{\circ}C$                        |          | 500  |     | μA    |

|                            | Cate to source forward lookage       | V <sub>GS</sub> = 6V                                                       |          | 2    | 200 |       |

| I <sub>GSS</sub>           | Gate-to-source forward leakage       | $V_{GS} = 6V$ $T_J = 125^{\circ}C$                                         |          | 50   |     | μA    |

|                            | Gate-to-source reverse leakage       | V <sub>GS</sub> = -4V                                                      |          | 0.1  | 200 |       |

| V <sub>GS(TH)</sub>        | Gate threshold voltage               | $V_{DS} = V_{GS}$ , $I_D = 19mA$                                           | 0.9      | 1.1  | 2.1 | V     |

| R <sub>DS(on)</sub>        | Drain-source On-state resistance (3) | V <sub>GS</sub> = 5V, I <sub>D</sub> = 50A                                 |          | 1.5  | 1.8 | mΩ    |

| V <sub>SD</sub>            | Source-drain forward voltage         | V <sub>GS</sub> = 0V, I <sub>S</sub> = 5A                                  |          | 1.8  |     | V     |

| DYNAMIC                    | (4)                                  |                                                                            | <u> </u> |      |     |       |

| C <sub>ISS</sub>           | Input capacitance                    | V <sub>DS</sub> = 50V, V <sub>GS</sub> = 0V                                |          | 2350 |     |       |

| C <sub>OSS</sub>           | Output capacitance                   | V <sub>DS</sub> = 50V, V <sub>GS</sub> = 0V                                |          | 1010 |     | ĺ     |

| C <sub>RSS</sub>           | Reverse transfer capacitance         | V <sub>DS</sub> = 50V, V <sub>GS</sub> = 0V                                |          | 14   |     | pF    |

| C <sub>OSS(ER)</sub>       | Energy related Coss                  | V <sub>DS</sub> = 0V to 50V, V <sub>GS</sub> = 0V                          |          | 1415 |     |       |

| C <sub>OSS(TR)</sub>       | Time related Coss                    | V <sub>DS</sub> = 0V to 50V, V <sub>GS</sub> = 0V                          |          | 2000 |     |       |

| R <sub>G</sub>             | Gate resistance                      | f = 5MHz, open drain                                                       |          | 0.73 |     | Ω     |

| $Q_{G}$                    | Total gate charge                    | $V_{DS} = 0V$ to 50V, $V_{GS} = 5V$ , $I_D = 50A$                          |          | 19   |     |       |

| Q <sub>GS</sub>            | Gate-to-source charge                | $V_{DS} = 0V \text{ to } 50V, V_{GS} = 5V,$ $I_D = 50A$                    |          | 4.2  |     | nC    |

| $Q_{\overline{GD}}$        | Gate-to-drain charge                 | $V_{DS} = 0V$ to 50V, $V_{GS} = 5V$ , $I_D = 50A$                          |          | 3    |     |       |

| V <sub>Plat</sub>          | Gate plateau voltage                 | V <sub>DS</sub> = 50V, V <sub>GS</sub> = 0V to 5V,<br>I <sub>D</sub> = 50A |          | 1.9  |     | V     |

| Q <sub>GD(TH)</sub>        | Gate charge at threshold             | $V_{DS} = 0V \text{ to } 50V, V_{GS} = 5V,$ $I_D = 50A$                    |          | 2.4  |     |       |

| Q <sub>OSS</sub>           | Output charge                        | V <sub>DS</sub> = 0V to 50V, V <sub>GS</sub> = 0V                          |          | 100  |     | nC    |

| Q <sub>rr</sub>            | Reverse recovery charge              | V <sub>DS</sub> = 50V, I <sub>S</sub> = 50A                                |          | 0    |     |       |

#### Notes

- Provided as measure of robustness under abnormal operating conditions and not recommended for normal operation.

- 2.  $R_{\theta ja}$  is determined with the device on FR4 PCB (2s2p with thermal vias) defined in accordance with JEDEC standards. PCB is mounted in horizontal position without air stream cooling.

- 3. RDS(on) is measured without prior drain bias or switching stress.

- 4. Guaranteed by design.

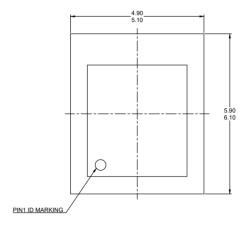

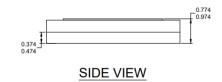

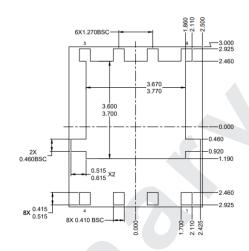

# Package Dimensions, En-FCLGA 5mm×6mm

# Package Reference

#### **BOTTOM VIEW**

- NOTE:

1) ALL DIMENSIONS ARE IN MILLIMETERS.

2) LEAD COPLANARITY SHALL BE 0.08MILLIMETERS MAX.

3) JEDEC REFERENCE IS MO-220.

4) DRAWING IS NOT TO SCALE.

# Pin Configuration:

# Marking Reference:

**TOP-Side View**

| Row  | Description   | Example |

|------|---------------|---------|

| Row1 | Company name  | INN     |

| Row2 | Product code  | XXX     |

| Row3 | Date code     | YYWW    |

| Row4 | Lot ID        | XXX     |

| Row5 | Lot ID+Subcon | XXX     |

Rev. 1.0 May 2025 Page 3 of 5 www.aosmd.com

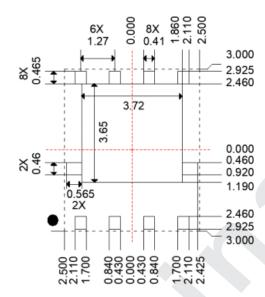

### Land Pattern, En-FCLGA 5mm×6mm

### Recommended Land Pattern

Unit: mm

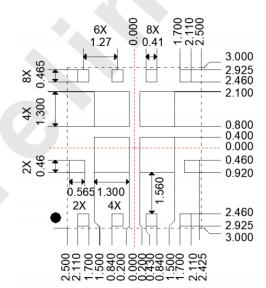

# Recommended Stencil Drawing

Unit: mm

Rev. 1.0 May 2025 **www.aosmd.com** Page 4 of 5

#### Part Marking

#### AOFG018V10GA1

#### LEGAL DISCLAIMER

Applications or uses as critical components in life support devices or systems are not authorized. Alpha and Omega Semiconductor does not assume any liability arising out of such applications or uses of its products. AOS reserves the right to make changes to product specifications without notice. It is the responsibility of the customer to evaluate suitability of the product for their intended application. Customer shall comply with applicable legal requirements, including all applicable export control rules, regulations and limitations.

AOS' products are provided subject to AOS' terms and conditions of sale which are set forth at: http://www.aosmd.com/terms and conditions of sale

#### LIFE SUPPORT POLICY

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

As used herein:

which, (a) are intended for surgical implant into the body or device, or system whose failure to perform can be reasonably (b) support or sustain life, and (c) whose failure to perform expected to cause the failure of the life support device or when properly used in accordance with instructions for use system, or to affect its safety or effectiveness. provided in the labeling, can be reasonably expected to result in a significant injury of the user.

1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support,

Rev. 1.0 May 2025 www.aosmd.com Page 5 of 5